## ОЗУ статическое с портами ввода вывода 1642PK1УБМ

Микросхема 1642РК1УБМ представляет собой двухпортовое статическое ОЗУ емкостью 64К (8Кх8) с двумя независимыми портами с раздельным управлением, адресом и выводами вход/выход, которые позволяют осуществить независимый, асинхронный доступ для чтения или записи по любому адресу в памяти. Применяется как самостоятельное двухпортовое ОЗУ 64К или как сочетание ведущее/ведомое двухпортовое ОЗУ для 16-ти и более разрядных систем. Микросхема предназначена для использования в высокопроизводительных системах обработки информации и устройствах управления специального применения. Изготавливается в 64-выводном корпусе типа Н18.64-3В, имеющем технологические перемычки расположенные между 24 и 25 и между 56 и 57 выводами. **Прототип IDT7005 ф. IDT**

#### Назначение выводов

| Номер вывода | Обозначение         | Назначение                            | Направление |

|--------------|---------------------|---------------------------------------|-------------|

| 01           | DI/DO <sub>2L</sub> | Бит 2 Данных левого порта             | вход /выход |

| 02           | DI/DO <sub>3L</sub> | Бит 3 Данных левого порта             | вход /выход |

| 03           | DI/DO <sub>4L</sub> | Бит 4 Данных левого порта             | вход /выход |

| 04           | DI/DO <sub>5L</sub> | Бит 5 Данных левого порта             | вход /выход |

| 05           | GND                 | Общий вывод                           |             |

| 06           | DI/DO <sub>6L</sub> | Бит 6 Данных левого порта             | вход /выход |

| 07           | DI/DO <sub>7L</sub> | Бит 7 Данных левого порта             | вход /выход |

| 08           | $V_{CC}$            | Вывод источника питания               |             |

| 09           | GND                 | Общий вывод                           |             |

| 10           | DI/DO <sub>0R</sub> | Бит 0 Данных правого порта            | вход /выход |

| 11           | DI/DO <sub>1R</sub> | Бит 1 Данных правого порта            | вход /выход |

| 12           | DI/DO <sub>2R</sub> | Бит 2 Данных правого порта            | вход /выход |

| 13           | $V_{CC}$            | Вывод питания от источника напряжения |             |

### Назначение выводов (продолжение)

| Номер вывода | Обозначение                | Назначение                               | Направление |

|--------------|----------------------------|------------------------------------------|-------------|

| 14           | DI/DO <sub>3R</sub>        | Бит 3 Данных правого порта               | вход /выход |

| 15           | DI/DO <sub>4R</sub>        | Бит 4 Данных правого порта               | вход /выход |

| 16           | DI/DO <sub>5R</sub>        | Бит 5 Данных правого порта               | вход /выход |

| 17           | DI/DO <sub>6R</sub>        | Бит 6 Данных правого порта               | вход /выход |

| 18           | DI/DO <sub>7R</sub>        | Бит 7 Данных правого порта               | вход /выход |

| 19           | $OE_R$                     | Запрет вывода правого порта              | вход        |

| 20           | $WR/RD_R$                  | Чтение/запись правого порта              | вход        |

| 21           | $SEM_R$                    | Разрешение работы семафора правого порта | вход        |

| 22           | $CE_R$                     | Вход сигнала разрешения правого порта    | вход        |

| 23           | NC                         | Вывод свободный                          |             |

| 24           | GND                        | Общий вывод                              |             |

| 25           | $A_{12R}$                  | Бит 12 адреса правого порта              | вход        |

| 26           | $A_{11R}$                  | Бит 11 адреса правого порта              | вход        |

| 27           | $A_{10R}$                  | Бит 10 адреса правого порта              | вход        |

| 28           | $A_{9R}$                   | Бит 9 адреса правого порта               | вход        |

| 29           | ${ m A_{8R}}$              | Бит 8 адреса правого порта               | вход        |

| 30           | $\mathrm{A}_{7\mathrm{R}}$ | Бит 7 адреса правого порта               | вход        |

| 31           | $A_{6R}$                   | Бит 6 адреса правого порта               | вход        |

| 32           | ${ m A}_{5 m R}$           | Бит 5 адреса правого порта               | вход        |

| 33           | $\mathrm{A}_{4\mathrm{R}}$ | Бит 4 адреса правого порта               | вход        |

| 34           | $A_{3R}$                   | Бит 3 адреса правого порта               | вход        |

| 35           | $A_{2R}$                   | Бит 2 адреса правого порта               | вход        |

| 36           | $A_{1R}$                   | Бит 1 адреса правого порта               | вход        |

| 37           | $A_{0R}$                   | Бит 0 адреса правого порта               | вход        |

| 38           | $INT_R$                    | Прерывание правого порта                 | выход       |

| 39           | BUSYR                      | Busy правого порта                       | вход /выход |

| 40           | M/S                        | Ведущий/ведомый                          | вход        |

### Назначение выводов (продолжение)

| Номер вывода | Обозначение                | Назначение                              | Направление |

|--------------|----------------------------|-----------------------------------------|-------------|

| 41           | GND                        | Общий вывод                             |             |

| 42           | $BUSY_L$                   | Виѕу левого порта                       | вход /выход |

| 43           | $INT_{L}$                  | Прерывание левого порта                 | выход       |

| 44           | $\mathrm{A}_{\mathrm{0L}}$ | Бит 0 адреса левого порта               | вход        |

| 45           | $A_{1L}$                   | Бит 1 адреса левого порта               | вход        |

| 46           | ${ m A}_{ m 2L}$           | Бит 2 адреса левого порта               | вход        |

| 47           | $A_{3L}$                   | Бит 3 адреса левого порта               | вход        |

| 48           | ${ m A_{4L}}$              | Бит 4 адреса левого порта               | вход        |

| 49           | ${ m A}_{ m 5L}$           | Бит 5 адреса левого порта               | вход        |

| 50           | ${ m A}_{ m 6L}$           | Бит 6 адреса левого порта               | вход        |

| 51           | ${ m A}_{7L}$              | Бит 7 адреса левого порта               | вход        |

| 52           | $A_{8L}$                   | Бит 8 адреса левого порта               | вход        |

| 53           | $A_{9L}$                   | Бит 9 адреса левого порта               | вход        |

| 54           | $A_{10L}$                  | Бит10 адреса левого порта               | вход        |

| 55           | $A_{11L}$                  | Бит11 адреса левого порта               | вход        |

| 56           | $A_{12L}$                  | Бит12 адреса левого порта               | вход        |

| 57           | $V_{CC}$                   | Вывод питания от источника напряжения   |             |

| 58           | N/C                        | Вывод свободный                         |             |

| 59           | $CE_{L}$                   | Вход сигнала разрешения левого порта    | вход        |

| 60           | $SEM_L$                    | Разрешение работы семафора левого порта | вход        |

| 61           | WR/RD <sub>L</sub>         | Чтение/запись левого порта              | вход        |

| 62           | $OE_L$                     | Запрет вывода левого порта              | вход        |

| 63           | DI/DO0L                    | Бит 0 Данных левого порта               | вход /выход |

| 64           | DI/DO1L                    | Бит 1 Данных левого порта               | вход /выход |

#### Предельные режимы

| Ogomowowa         | Папаматру                                                     | Нор      | Единица  |           |

|-------------------|---------------------------------------------------------------|----------|----------|-----------|

| Обозначение       | Параметры                                                     | не менее | не более | измерения |

| U <sub>TERM</sub> | Напряжение питания                                            | -0.5     | 7        | В         |

| Ui                | Входное напряжение                                            | -0.5     | 7        | В         |

| T                 | Температурный диапазон хранения без подачи напряжения питания | -60      | 150      | °C        |

| Tamb              | Температура окружающей среды при подаче напряжения питания.   | -60      | 135      | °C        |

| $I_{O}$           | Выходной ток                                                  | -50      | 50       | мА        |

### Предельно допустимые режимы

| Обозначение | Параметры                            | Ho       | Единица  |                      |

|-------------|--------------------------------------|----------|----------|----------------------|

| Ооозначение | параметры                            | не менее | не более | измерения            |

| Ucc         | Напряжение питания                   | 4.5      | 5.5      | В                    |

| $V_{ m IH}$ | Входное напряжение высокого уровня   | 2.2      | 6.0      | В                    |

| $ m V_{IL}$ | Входное напряжение низкого уровня    | 0        | 0.8      | В                    |

| $I_{OL}$    | Выходной ток низкого уровня          |          | 4        | мА                   |

| $I_{OH}$    | Выходной ток высокого уровня         | _        | -4       | мА                   |

| T           | Рабочий температурный диапазон среды | -60      | +125     | $^{\circ}\mathrm{C}$ |

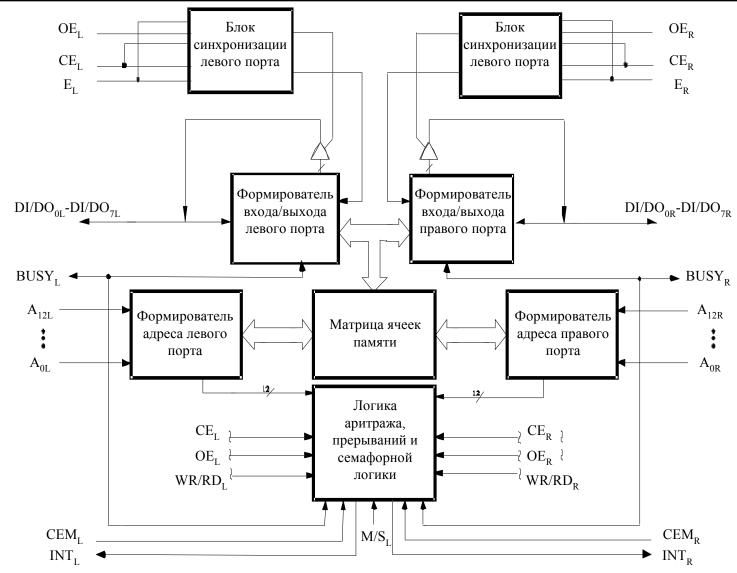

Структурная схема микросхемы

# Статические параметры

| Обозначение        | Парамотру                                                         | Романи изморония                                                                                                                                                                 | Но       | рма      | Единица   |  |

|--------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------|--|

| Ооозначение        | Параметры                                                         | Режим измерения                                                                                                                                                                  | не менее | не более | измерения |  |

| $I_{LI}$           | Ток утечки по входу                                               | $V_{IN}=0 \div Ucc Ucc=5.5B$                                                                                                                                                     |          | 10       | мкА       |  |

| $I_{LO}$           | Ток утечки по выходу                                              | $V_{OUT}=0 \div Ucc Ucc=5.5B$                                                                                                                                                    | -        | 10       | MKA       |  |

| $ m V_{OH}$        | Выходное напряжение высокого уровня                               | $I_{OH}$ =-4 <sub>M</sub> A                                                                                                                                                      | 2.4      | -        | В         |  |

| $ m V_{OL}$        | Выходное напряжение низкого уровня                                | $I_{OL}$ =4 MA                                                                                                                                                                   |          | 0.4      | В         |  |

| $I_{CC}$           | Динамический рабочий ток (оба порта активные)                     | CE=V <sub>IL</sub> ,Выходы открыты<br>SEM=V <sub>IL</sub> , f=fMAX(1)                                                                                                            |          | 300      |           |  |

| $I_{SB1}$          | Ток хранения (Оба порта –<br>входы с TTL уровнями)                | CE <sub>L</sub> =CE <sub>R</sub> =V <sub>IH</sub> , SEM <sub>R</sub> =SEM <sub>L</sub> =V <sub>IH</sub><br>f=fMAX <sup>(1)</sup>                                                 |          | 80       |           |  |

| $I_{\mathrm{SB2}}$ | Ток хранения (Один порт – входы с TTL уровнями)                   | $CE "A"=V_{IL \ II} CE "B"=V_{IH}^{(3)}$ . Выходы активного порта открыты. $f=14M\Gamma_{II} SEM_R=SEM_L=V_{IH}$                                                                 |          | 190      |           |  |

| $ m I_{SB3}$       | Полный ток хранения<br>(Оба порта – все входы с<br>КМОП уровнями) | Оба порта: $CE_L \text{ и } CE_R \geq Vcc\text{-}0.2B$ $V_{IN} \geq Vcc\text{-}0.2B \text{ или } V_{IN} \leq 0.2B,  f\text{=}0^{(2)},$ $SEM_R\text{=}SEM_L \geq Vcc\text{-}0.2B$ | -        | 30       | мА        |  |

| $ m I_{SB4}$       | Полный ток хранения (Один порт – все входы с КМОП уровнями)       | $CE$ "A" $\leq 0.2B$ и $CE$ "B" $\geq Vcc$ -0.2B $SEM_R = SEM_L \geq Vcc$ -0.2B $V_{IN} \geq Vcc$ -0.2B или $V_{IN} \leq 0.2B$ Выходы активного порта открыты $f = fMAX^{(1)}$   |          | 175      |           |  |

| $C_{IN}$           | Входная емкость                                                   | V <sub>IN</sub> =0 В f=1МГц, T=25°С (3)                                                                                                                                          |          | 9        | пФ        |  |

| $C_{out}$          | Выходная емкость                                                  | $V_{OUT}=0 \text{ B f}=1\text{M}\Gamma\text{II}, T=25^{\circ}\text{C (3)}$                                                                                                       |          | 10       | ПΨ        |  |

| ФК                 | Функциональный контроль (4)                                       | Ucc=4.55.5B F=14МГц                                                                                                                                                              |          |          |           |  |

#### Примечания:

- 1. f = 0 означает отсутствие переключения адресов или цепей управления.

- 2. Порт "А" может быть или левый или правый порт. Порт "В" есть порт противоположный "А" порту.

- 3 Параметр гарантируется квалифицированными испытаниями.

- 4 В случае если функциональный контроль проводят на максимальной рабочей частоте (F=14МГц) проверку динамических параметров допускается не проводить.

- 5 Нормы на параметры и режимы измерений таблицы 4 могут уточняться в ходе ОКР в технически обоснованных случаях.

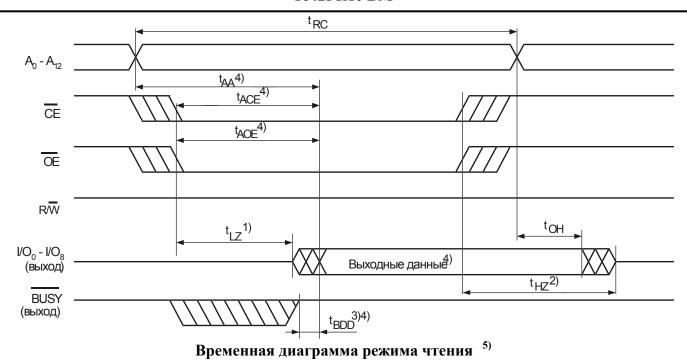

#### Динамические параметры цикла чтения (Ucc=4.5B,T= -60 ÷ 125 °C)

| Наименование параметра                                                                      | Обозначение        | Нор      | Примечание |            |

|---------------------------------------------------------------------------------------------|--------------------|----------|------------|------------|

| паименование параметра                                                                      | параметра          | не менее | не более   | примечание |

| Время цикла чтения, нс                                                                      | t <sub>CY R</sub>  | 70       | _          | _          |

| Время выборки адреса                                                                        | $t_{A(A)}$         |          | 70         |            |

| Время выбора                                                                                | $t_{CS}$           | _        | 70         | 1          |

| Время выборки разрешения выхода                                                             | $t_{A(OE)}$        |          | 35         | _          |

| Сохранение выхода по смене адреса                                                           | $t_{OH}$           | 3        | _          |            |

| Время выхода по Low-Z                                                                       | $t_{LZ}$           | 3        |            | 2          |

| Время выхода по High-Z                                                                      | $t_{\mathrm{HZ}}$  | _        | 30         | 2          |

| Время включения мощности хранения по СЕ                                                     | $t_{\mathrm{PU}}$  | 0        |            |            |

| Время отключения мощности хранения по СЕ                                                    | $t_{\mathrm{PD}}$  | _        | 50         |            |

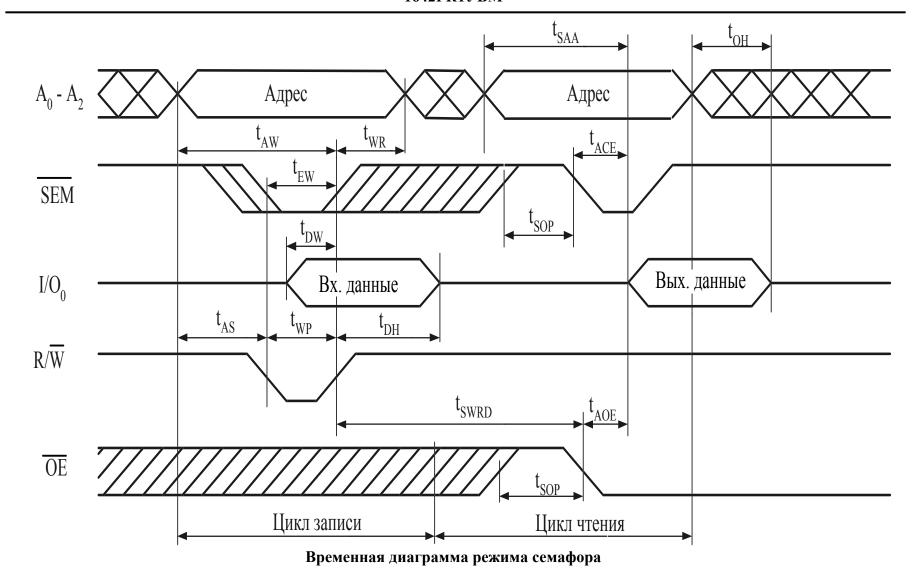

| Импульс обновления сигнального флага ( $\overline{\text{OE}}$ или $\overline{\text{SEM}}$ ) | $t_{SOP}$          | 15       | _          | _          |

| Время доступа сигнального адреса                                                            | $t_{\mathrm{SAA}}$ | _        | 70         |            |

#### Примечания

- 1 Для доступа к ОЗУ  $CE = V_{IL}$  и  $SEM = V_{IH}$ . Для доступа к флаг-сигналу  $CE = V_{IH}$  и  $SEM = V_{IL}$

- 2 Время задержки измеряется на уровне  $\pm$  500 мВ от низкого или высокого уровня напряжения выходного сигнала

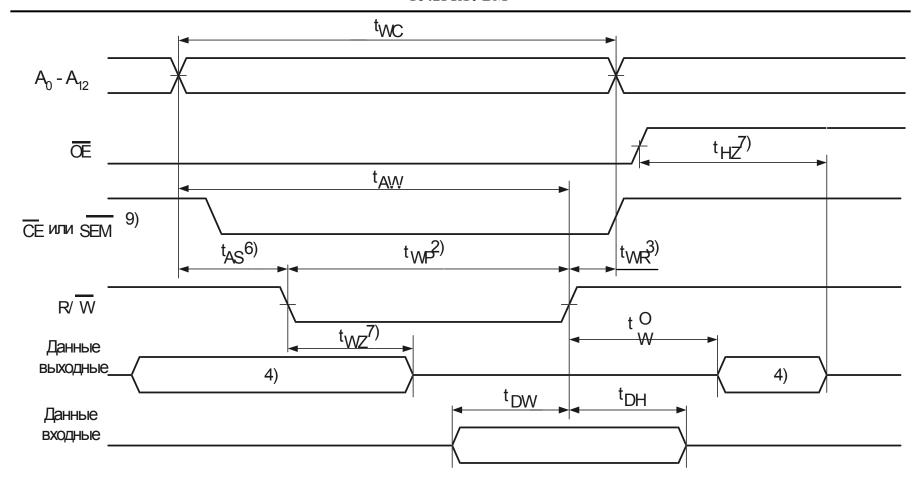

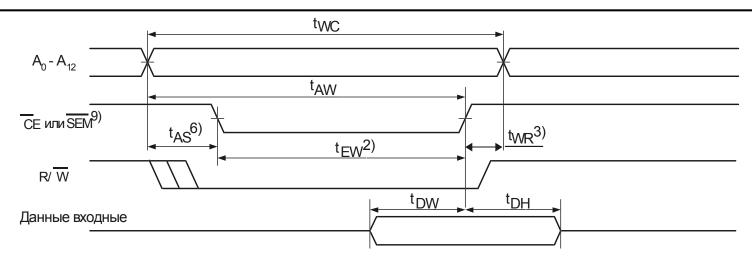

#### Динамические параметры цикла записи (Ucc=4.5÷5.5B,T= -60 ÷ 125 °C)

| Наименование параметра                  | Обозначение        | Норм     | 1а, нс   | Приме |

|-----------------------------------------|--------------------|----------|----------|-------|

| паименование параметра                  | параметра          | не менее | не более | чание |

| Время цикла записи                      | t <sub>CY W</sub>  | 70       |          | _     |

| Разрешение кристалла к концу записи     | $t_{\mathrm{EW}}$  | 50       |          | 1     |

| Значение адреса к концу записи          | $t_{AW}$           | 50       |          | _     |

| Время предустановки адреса              | $t_{ m AS}$        | 0        | _        | 1     |

| Ширина импульса записи                  | $t_{ m WP}$        | 50       |          |       |

| Время восстановления записи             | $t_{\mathrm{WR}}$  | 0        |          | _     |

| Значение данных к концу записи          | $t_{ m DW}$        | 40       |          |       |

| Выходное время High-Z                   | $t_{ m HZ}$        | _        | 30       | 2     |

| Время удержания данных                  | $t_{ m DH}$        | 0        | _        | _     |

| Разрешение записи к выходу High-Z       | $t_{ m WZ}$        | _        | 30       |       |

| Включение выхода от конца записи        | $t_{OW}$           | 0        |          | 2     |

| Время БЕМ флага от записи к чтению      | $t_{ m SWRD}$      | 5        | _        |       |

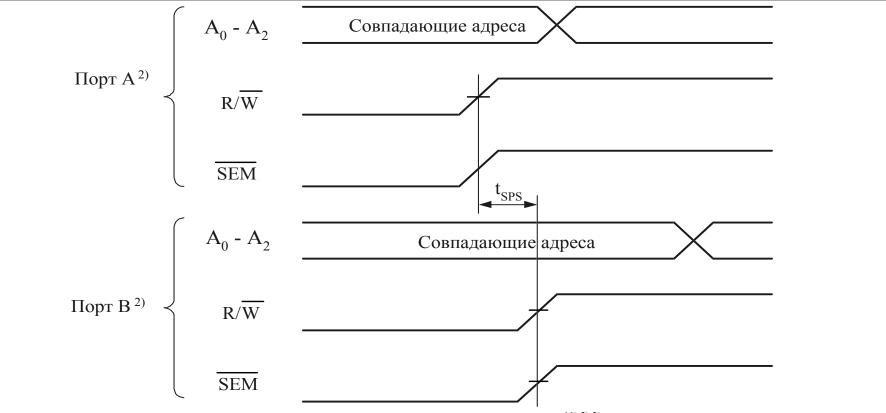

| Окно содержимого $\overline{SEM}$ флага | $t_{\mathrm{SPS}}$ | 5        |          | _     |

### Примечания

1 Для доступа к ОЗУ  $\overline{CE} = V_{IL}$  и  $\overline{SEM} = V_{IH}$ . Для доступа к флаг-сигналу  $\overline{CE} = V_{IH}$  и  $\overline{SEM} = V_{IL}$

2 Время задержки измеряется на уровне  $\pm$  500 мВ от низкого или высокого уровня напряжения выходного сигнала

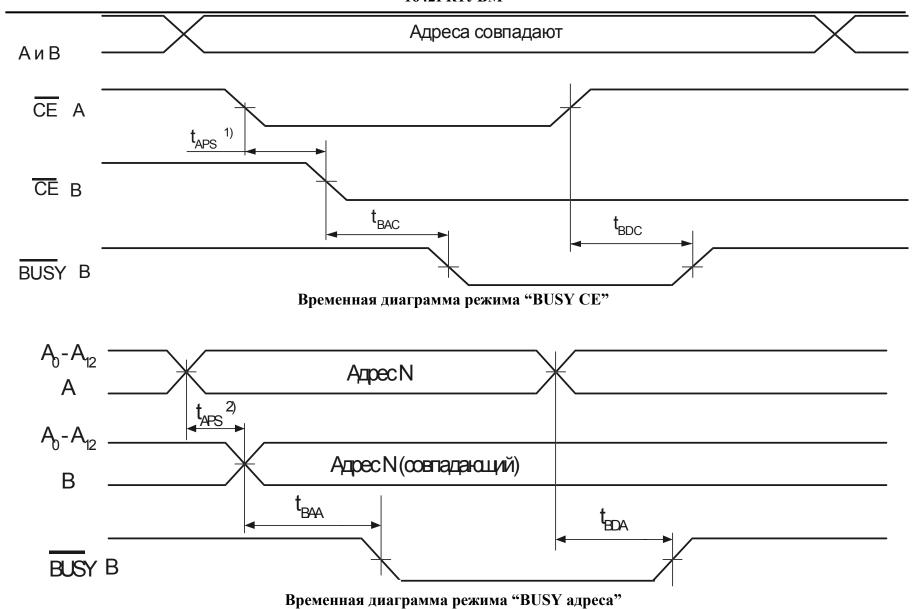

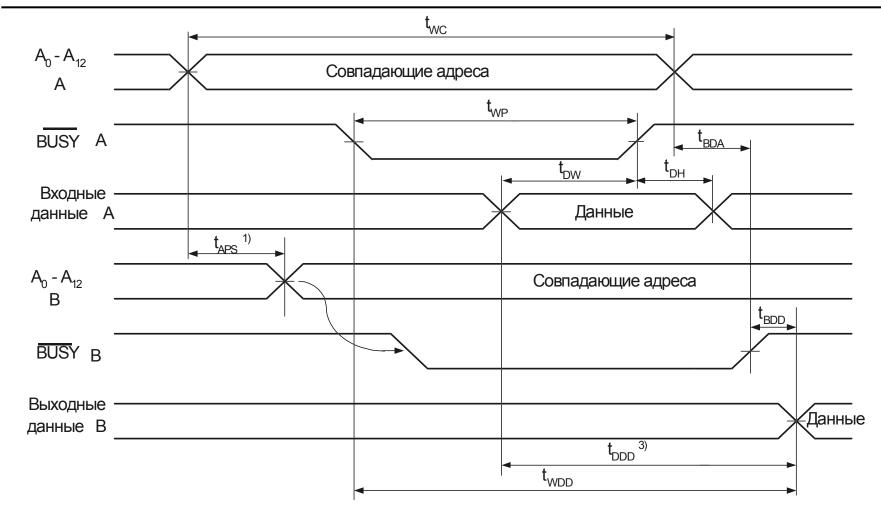

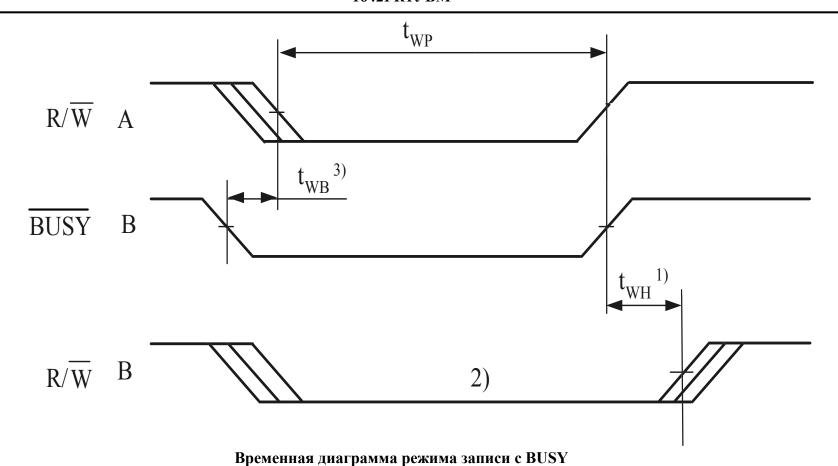

# Динамические параметры в режиме $\overline{BUSY}$ (Ucc=4.5÷5.5B,T= -60 ÷ 125 °C)

| <b>Наимонорамие нарометра</b>                          | Обозначение                                             | Норм     | 1а, нс   |

|--------------------------------------------------------|---------------------------------------------------------|----------|----------|

| Наименование параметра                                 | параметра                                               | не менее | не более |

| Временная диаграмма                                    | $\overline{BUSY} \ (M/\overline{S} = V_{IH})$           | _        | _        |

| Время доступа $\overline{BUSY}$ от совпадения адреса   | $t_{ m BAA}$                                            | _        | 45       |

| Время запрета $\overline{BUSY}$ от несовпадения адреса | $t_{ m BDA}$                                            |          | 40       |

| Время доступа $\overline{BUSY}$ от Low разрешения      | $t_{\mathrm{BAC}}$                                      |          | 40       |

| кристалла                                              |                                                         |          |          |

| Время доступа $\overline{BUSY}$ от High разрешения     | $t_{ m BDC}$                                            |          | 35       |

| кристалла                                              |                                                         |          |          |

| Время установки арбитража приоритета                   | $t_{ m APS}$                                            | 5        |          |

| Запрет $\overline{BUSY}$ к значению данных             | $t_{ m BDD}$                                            | _        | 45       |

| Удержание записи после $\overline{BUSY}$               | $t_{ m WH}$                                             | 25       | _        |

| Временная диаграмма                                    | $\overline{BUSY}$ (M/ $\overline{S}$ =V <sub>IL</sub> ) |          |          |

| $\overline{BXOJ}$ $\overline{BUSY}$ к записи           | $t_{ m WB}$                                             | 0        | _        |

| Удержание записи после $\overline{BUSY}$               | $t_{ m WH}$                                             | 25       |          |

| Временная диаграмма за                                 | держки Порт-Порт                                        |          |          |

| Импульс записи к задержке данных                       | $t_{ m WDD}$                                            | _        | 95       |

| Значение данных записи к задержке данных               | $t_{ m DDD}$                                            |          | 80       |

| чтения                                                 |                                                         |          |          |

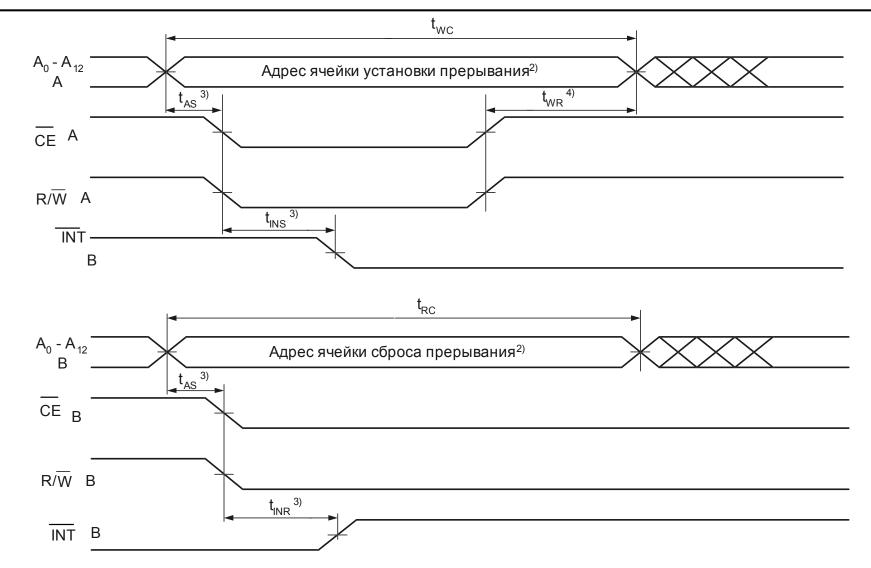

### Динамические параметры в режиме прерывания (Ucc=4.5÷5.5B,T= -60 ÷ 125 °C)

| Наименование параметра      | Обозначение   | Но       | рма, нс  |

|-----------------------------|---------------|----------|----------|

| паименование параметра      | параметра     | не менее | не более |

| Время предустановки адреса  | $t_{AS}$      | 0        | _        |

| Время восстановления записи | $t_{ m WR}$   | 0        |          |

| Время установки прерывания  | $t_{ m INS}$  | _        | 50       |

| Время сброса прерывания     | $t_{\rm INR}$ |          | 50       |

### Таблица истинности режимов чтения, записи

|    | B                                                        | ход |     | Вход/выход   | D                                |  |  |

|----|----------------------------------------------------------|-----|-----|--------------|----------------------------------|--|--|

| CE | WR/RD                                                    | ŌĒ  | SEM | DI/DO        | Режим                            |  |  |

| Н  | X                                                        | X   | Н   | Z            | Пониженного потребления мощности |  |  |

| L  | L                                                        | X   | Н   | Вход данных  | Запись                           |  |  |

| L  | Н                                                        | L   | Н   | Выход данных | Чтение                           |  |  |

| X  | Х Х Н Х Z Состояние с высоким импедансом                 |     |     |              |                                  |  |  |

| П  | Примечание – Адреса правого и левого портов не совпадают |     |     |              |                                  |  |  |

#### Таблица истинности режима семафора чтения, записи

|                        | Bxc        | DД |     | Выход              | Darrens                                    |

|------------------------|------------|----|-----|--------------------|--------------------------------------------|

| $\overline{\text{CE}}$ | WR/RD      | ŌE | SEM | DI/DO <sub>1</sub> | Режим                                      |

| Н                      | Н          | L  | L   | Выход данных       | Чтение (контроль) семафора выходных данных |

| Н                      | $\uparrow$ | X  | L   | Вход данных        | Запись DI/DO <sub>1</sub> в флаг семафора  |

| L                      | X          | X  | L   | _                  | запрещено                                  |

Примечание – Имеются 8 флагов семафора, записываемые через  $DI/DO_1$  и считываемые из  $DI/DO_1 - DI/DO_8$ . Эти флаги кодируются адресами  $A_0 - A_2$

#### Таблица истинности режима прерывания 1)

|           | юрт                               | Правый порт                       |                      |                                    |                    |                            | Φ                          |                    |                             |                                          |

|-----------|-----------------------------------|-----------------------------------|----------------------|------------------------------------|--------------------|----------------------------|----------------------------|--------------------|-----------------------------|------------------------------------------|

| $WR/RD_L$ | $\overline{\text{CE}}_{\text{L}}$ | $\overline{\text{OE}}_{\text{L}}$ | $A_{0L}$ - $A_{12L}$ | $\overline{\text{INT}}_{\text{L}}$ | WR/RD <sub>R</sub> | $\overline{\text{CE}}_{R}$ | $\overline{\text{OE}}_{R}$ | $A_{0R} - A_{12R}$ | $\overline{\text{INT}}_{R}$ | Функция                                  |

| L         | L                                 | X                                 | 111111111            | X                                  | X                  | X                          | X                          | X                  | L 3)                        | Установка флага прерывания правого порта |

| X         | X                                 | X                                 | X                    | X                                  | X                  | L                          | L                          | 111111111          | $H^{2)}$                    | Сброс флага прерывания правого порта     |

| X         | X                                 | X                                 | X                    | L 3)                               | L                  | L                          | X                          | 111111110          | X                           | Установка флага прерывания левого порта  |

| X         | L                                 | L                                 | 111111110            | $H^{2)}$                           | X                  | X                          | X                          | X                  | X                           | Сброс флага прерывания левого порта      |

$<sup>^{1)}</sup>$  В исходном состоянии входы  $\overline{BUSY_L} = BUSY_R = V_{IH}$ . Выходы  $\overline{INT}_R$  и  $\overline{INT}_L$  должны быть установлены в исходное состояние при включении питания

$<sup>^{2)}</sup>$  Если вход BUSY<sub>R</sub> = V<sub>IL</sub> изменения не происходят

$<sup>^{3)}</sup>$  Если вход BUSY<sub>L</sub> = V<sub>IL</sub> изменения не происходят

#### Таблица истинности арбитража BUSY

|                                   | Bxo                        | ды                                                      | Вых      | оды                  |                                |  |

|-----------------------------------|----------------------------|---------------------------------------------------------|----------|----------------------|--------------------------------|--|

| $\overline{\text{CE}}_{\text{L}}$ | $\overline{\text{CE}}_{R}$ | ${ m A_{0L}}{ m - A_{12L}} \ { m A_{0R}}{ m - A_{12R}}$ | BUSY L1) | BUSY <sub>R</sub> 1) | Функция                        |  |

| X                                 | X                          | не совпадают                                            | Н        | Н                    | нормальный                     |  |

| Н                                 | X                          | совпадают                                               | Н        | Н                    | нормальный                     |  |

| X                                 | H                          | совпадают                                               | Н        | Н                    | нормальный                     |  |

| L                                 | L                          | совпадают                                               | 2)       | 2)                   | запись запрещена <sup>3)</sup> |  |

$<sup>\</sup>overline{BUSY}_{L}$ ,  $\overline{BUSY}_{R}$  являются выходами, когда установлены , как «ведущие». Оба вывода являются входами, когда установлены, как «ведомые». Вывод  $\overline{BUSY}$  двухтактный, не является выходом с открытым стоком. В состоянии «ведомого» вход  $\overline{BUSY}$  извне запрещает запись в ячейку

H – если входы противоположного порта устанавливаются после адресов и входов разрешения этого порта.

Если время установки арбитража приоритета  $t_{APS}$  не достигнуто, один из выходов BUSY  $_L$  или  $\overline{BUSY}_R$  станет L, оба выхода одновременно не могут перейти в состояние логического "0"

<sup>&</sup>lt;sup>2)</sup> L – если входы противоположного порта имеют приоритет по адресам или входам разрешения этого порта.

$<sup>^{3)}</sup>$  Запись в левый (правый) порт запрещается извне, подачей на вывод  $\overline{BUSY}_L$  ( $\overline{BUSY}_R$ ) уровня логического 0, независимо от состояния остальных логических входов

$^{1)}$  Параметр зависит от того, какой из сигналов  $\overline{\rm OE}\,$  или  $\overline{\rm CE}\,$  установится последним

$\overline{^{2)}}$  Параметр зависит от того, какой из сигналов  $\overline{OE}$  или  $\overline{CE}$  последним выйдет из режима

<sup>3)</sup> Задержка необходима только в случае, когда противоположный порт производит запись в ячейки с тем же адресом. Для одновременного чтения работа BUSY не влияет на выходные данные

<sup>4)</sup> Начало чтения выходных данных зависит от того, какое событие произойдет последним:  $t_{AA}$ ,  $t_{ACE}$ ,  $t_{AOE}$  или  $t_{BDD}$

$5) \overline{\text{SEM}} = V_{\text{IH}}$

Временная диаграмма режима записи 1  $^{1)\,5)\,8}$

Временная диаграмма режима записи 2 1) 5)

- $^{*}$  1) Выводы  $R/\overline{W}$  или  $\overline{CE}$  должны оставаться высокими во время переключения адресов

- $^{2)}$  Запись может накладываться (перекрываться) ( $t_{EW}$ ,  $t_{WP}$ ) низким уровнем на выводе  $\overline{CE}$  и низким уровнем на выводе  $R/\overline{W}$  цикла записи в массив памяти

- $^{3)}$   $t_{WR}$  измеряется от ранее перешедшего в высокий уровень сигнала  $\overline{CE}$  или  $R/\overline{W}$  (или  $\overline{SEM}$  или  $R/\overline{W}$ ) в конце цикла записи

- <sup>4)</sup> В течение этого режима выводы DI/DO являются выходами и входные сигналы не должны применяться

- $^{5)}$  Если переход в низкий уровень выводов  $\overline{\text{CE}}$  и  $\overline{\text{SEM}}$  происходит одновременно, выходы сохраняют третье состояние (высокого импеданса)

- $^{6)}$  Время зависит от того, какой из сигналов  $\overline{\text{CE}}$  или  $R/\overline{W}$  установится последним

- $^{7)}$  Этот параметр гарантируется конструктивно, но не контролируется. Измеряется переход  $\pm$  500 мВ из устойчивого состояния по схеме, приведенной на рисунке A.8

- $^{8)}$  Если  $\overline{OE}$  остается низким в течение всего цикла записи, контролируемого  $R/\overline{W}$ , ширина импульса должна увеличиться на время  $t_{WP}$  или  $(t_{WZ}+t_{WD})$ , чтобы разрешить выводам DI/DO выключиться и данным разместиться на шине для ожидания  $t_{DW}$

- $^{9)}$  Для доступа к O3У  $\overline{\text{CE}} = V_{\text{IH}}, \ \overline{\text{SEM}} = V_{\text{IL}}$ . Для доступа к флаг-сигналу  $\overline{\text{CE}} = V_{\text{IH}}, \ \overline{\text{SEM}} = V_{\text{IL}}$ .  $t_{\text{EW}}$  должно перейти в любое состояние

Временная диаграмма режима BUSY порт-порт

Временная диаграмма режима прерывания

Временная диаграмма режима семафора<sup>\*1) 2) 3)</sup>

$<sup>^{*~1)}</sup>$  DI/DO<sub>L</sub> = DI/DO<sub>R</sub> = V<sub>IL</sub>,  $\overline{CE}_L = \overline{CE}_R = V_{IH}$ . Флаг семафора обоих портов свободен на начало цикла.

$<sup>^{2)}</sup>$  Динамические параметры одинаковы для левого и правого портов. Порт A может быть как левым портом, так и правым, порт B – противоположный порту A.

$<sup>^{3)}</sup>$  Параметр измеряется от вывода, R/  $\overline{W}_A$  или  $\overline{SEM}_A$  , переключившегося в высокий уровень, до вывода, R/  $\overline{W}_B$  или  $\overline{SEM}_B$  , переключившегося в высокий уровень.

<sup>4)</sup> Если время t<sub>SPS</sub> не достаточное, семафор установится для одного из портов, но не конкретный порт не гарантируется